UNIVERSITY OF GOTHENBURG

# **Game Boy Emulation**

# Emulating a Complex System

Bachelor's thesis in Computer Science and Engineering

Algot Axelzon Isak Lindgren Carl Lindh David Möller Andreas Palmqvist Arvid Rydberg

Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY UNIVERSITY OF GOTHENBURG Gothenburg, Sweden 2021

# BACHELOR'S THESIS 2021

# Game Boy Emulation

Emulating a Complex System

Algot Axelzon Isak Lindgren Carl Lindh David Möller Andreas Palmqvist Arvid Rydberg

UNIVERSITY OF GOTHENBURG

Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY UNIVERSITY OF GOTHENBURG Gothenburg, Sweden 2021 Game Boy Emulation Emulating a Complex System Algot Axelzon Isak Lindgren Carl Lindh David Möller Andreas Palmqvist Arvid Rydberg

$\ensuremath{\mathbb{O}}$  Algot Axelzon, Isak Lindgren, Carl Lindh, David Möller, Andreas Palmqvist, Arvid Rydberg 2021.

Supervisor: Roc R. Currius, Department of Computer Science and Engineering Examiner: Sven Knutsson, Department of Computer Science and Engineering

Bachelor's Thesis 2021 Department of Computer Science and Engineering Chalmers University of Technology and University of Gothenburg SE-412 96 Gothenburg Telephone +46 31 772 1000

Cover: Image of the original Game Boy from 1989. From [1]. Public Domain.

Gothenburg, Sweden 2021

# Abstract

This thesis studies the subject of system emulation through the development of a set of software microcontrollers and the assembling of them into a complex system. The specific system aimed to be emulated is the original Game Boy released in 1989. This requires the developers to reproduce specific hardware behaviour through software and therefore requires certain knowledge of the system which is to be emulated. While the Game Boy is a proprietary product owned by Nintendo, the produced system uses no copyrighted material.

Through the use of documentation provided by the reverse engineering of the original hardware done by members of the community, this thesis shows that an emulator can be created by combining a set of software microcontrollers. Moreover, it is concluded that while the academic interest in the emulation of simple systems might be limited, it could also could be used to generate interest in low-level programming.

Keywords: Emulation, Gameboy, Game Boy, C++, OpenGL, OpenAL, ImGui

v

# Sammandrag

Denna kandidatuppsats studerar systememulation genom att utveckla ett flertal mjukvarumikrokontroller som därefter kombineras för att tillsammans bilda ett komplext system. Det specifika systemet som emuleras är den första Game Boy-konsollen, släppt 1989. För att genomföra detta krävs det att utvecklarna reproducerar den specifika hårdvaran i mjukvara, vilket kräver viss kunskap om det ursprungliga systemet. Då Game Boy är en licensierad produkt, ägd av Nintendo, är det värt att notera att det framtagna systemet ej använder något upphovsrättssky-ddat material.

Dokumentationen som använts för att skapa denna emulator har tagits fram genom att demontera och undersöka originalhårdvaran. Detta har gjorts av ett flertal deltagare i en emulatorintresserad internetgemenskap. Avslutningsvis konstateras att det, trots det begränsade akademiska intresset för systememulering av enkla system, finns potential för att använda sig av det för att skapa intresse för lågnivåprogrammering.

Nyckelord: Emulering, Gameboy, Game Boy, C++, OpenGL, OpenAL, ImGui

# Acknowledgements

We would like to thank our supervisor Roc R. Currius for providing an initial project and for rigorous feedback regarding the writing of this report. During the project he also provided weekly guidance in our efforts to develop the emulator. Secondly we would like to thank Albin Johansson for providing thorough feedback on the code written for this project, which gave many valuable insights regarding style and general use of C++.

Algot Axelzon, Isak Lindgren, Carl Lindh, David Möller, Andreas Palmqvist, Arvid Rydberg, Gothenburg, June 2021

# Terminology

- ROM Read only memory. A memory which in the context of emulator development contains the game data.

- RAM Random access memory. As opposed to ROM, RAM can both be read from and written to. The data stored in RAM is however volatile the memory stores data only as long as it has power.

- 0x Using the 0x prefix indicates that the following value is to be interpreted as a hexadecimal value. For example the value 0xA0 is to be interpreted as 160.

- KiB/MiB KiB and MiB are used for Kibibyte and Mebibyte, they are of base two and are representing 1024 (2<sup>10</sup>) byte and 1 048 576 (2<sup>20</sup>) byte respectively.

- I/O Input/Output, used for describing units handling either input or output, such as a display or keyboard.

- Scanline The process of rendering a row of pixels to the display.

- CPU Central Processing Unit

- PPU Pixel Processing Unit, responsible for producing pixel data for the Game Boy's LCD.

- APU Audio Processing Unit, responsible for generating audio data.

- MMU Memory Management Unit, responsible for handling memory mapping within the emulator.

- Microcontroller A small computer on a single chip.

- Software microcontroller Software imitating the function of a microcontroller.

- Sprite A 2D bitmap representing an image.

- Joypad A device that connects the user's input with the system. In the context of the Game Boy this refers to four directional buttons and four action buttons.

# Contents

| Li       | st of | Figure | es                            | xiv  |

|----------|-------|--------|-------------------------------|------|

| Li       | st of | Tables | 5                             | xvi  |

| 1        | Intr  | oducti | on                            | 1    |

|          | 1.1   | Emula  | tors in general               | . 1  |

|          | 1.2   | An Int | troduction to the Game Boy    | . 1  |

|          | 1.3   | Purpos | se                            | . 4  |

|          | 1.4   | Delimi | itations                      | . 4  |

|          | 1.5   | Ethics |                               | . 5  |

| <b>2</b> | The   | ory    |                               | 6    |

|          | 2.1   | The C  | entral Processing Unit        | . 6  |

|          |       | 2.1.1  | Registers                     |      |

|          |       | 2.1.2  | Instruction set               | . 6  |

|          |       | 2.1.3  | Interrupts                    | . 7  |

|          | 2.2   | Memor  | ry and I/O devices            | . 9  |

|          |       | 2.2.1  | Boot ROM                      | . 9  |

|          |       | 2.2.2  | ROM                           | . 10 |

|          |       | 2.2.3  | Video RAM                     | . 10 |

|          |       | 2.2.4  | External RAM                  | . 10 |

|          |       | 2.2.5  | WRAM                          | . 10 |

|          |       | 2.2.6  | OAM RAM                       | . 10 |

|          |       | 2.2.7  | Joypad                        | . 11 |

|          |       | 2.2.8  | Timer                         | . 11 |

|          |       | 2.2.9  | HRAM                          | . 12 |

|          |       | 2.2.10 | Memory Bank Controllers       | . 13 |

|          | 2.3   | The P  | ixel Processing Unit          | . 15 |

|          |       | 2.3.1  | Composing the frame           | . 15 |

|          |       | 2.3.2  | The modes                     | . 18 |

|          |       | 2.3.3  | The registers                 | . 19 |

|          |       | 2.3.4  | Drawing the image             | . 21 |

|          |       | 2.3.5  | Direct Memory Access transfer | . 21 |

|          | 2.4   | The A  | udio Processing Unit          |      |

|          |       | 2.4.1  | The registers                 | . 22 |

|          |       | 2.4.2  | Events                        | . 24 |

|          |                      | 2.4.3 The audio data $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 24$            | 4 |

|----------|----------------------|------------------------------------------------------------------------------------------------------------|---|

| 3        | Too                  | ls and methodology 20                                                                                      | 6 |

|          | 3.1                  | Programming language                                                                                       | 6 |

|          | 3.2                  | Graphics and GUI                                                                                           | 6 |

|          | 3.3                  | Audio                                                                                                      | 6 |

|          | 3.4                  | Scrum                                                                                                      | 7 |

|          | 3.5                  | Plan                                                                                                       | 7 |

|          | 3.6                  | Architecture                                                                                               | 8 |

|          | 3.7                  | Testing                                                                                                    |   |

| 4        | $\operatorname{Res}$ | ults 30                                                                                                    | n |

| т        | 4.1                  | Architecture and Design                                                                                    |   |

|          | 4.2                  | The Central Processing Unit                                                                                |   |

|          | 4.2                  |                                                                                                            |   |

|          |                      | 4.2.1       Interrupts       31         4.2.2       Testing of the Central Processing Unit       33        |   |

|          | 4.3                  | 8                                                                                                          |   |

|          | 4.5                  | 2 0 0                                                                                                      |   |

|          |                      |                                                                                                            |   |

|          |                      | 0                                                                                                          |   |

|          | 4 4                  | 0 0                                                                                                        |   |

|          | 4.4                  | The Pixel Processing Unit                                                                                  |   |

|          |                      | 4.4.1 Timing                                                                                               |   |

|          |                      | 4.4.2 Basic operation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 3$                                 |   |

|          |                      | 4.4.3 Drawing                                                                                              |   |

|          |                      | 4.4.4 DMA transfer $\ldots$ $33$                                                                           |   |

|          |                      | 4.4.5 Testing of the Pixel Processing Unit                                                                 |   |

|          | 4.5                  | The Audio Processing Unit                                                                                  |   |

|          |                      | 4.5.1 The Audio Controller                                                                                 |   |

|          |                      | 4.5.2 Testing of the Audio Processing Unit                                                                 |   |

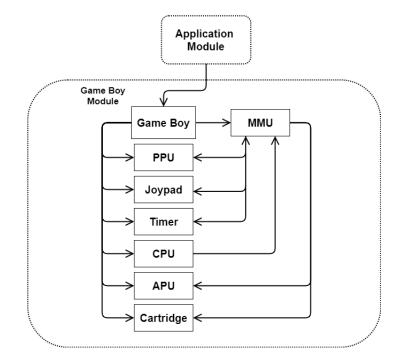

|          | 4.6                  | The Game Boy                                                                                               | 1 |

| <b>5</b> | Dise                 | cussion 42                                                                                                 | 2 |

|          | 5.1                  | Hardware                                                                                                   | 2 |

|          |                      | 5.1.1 The Central Processing Unit                                                                          | 2 |

|          |                      | 5.1.2 The Memory Management Unit                                                                           | 3 |

|          |                      | 5.1.3 The Pixel Processing Unit                                                                            | 3 |

|          |                      | 5.1.4 The Audio Processing Unit                                                                            | 4 |

|          | 5.2                  | Accuracy                                                                                                   | 5 |

|          |                      | 5.2.1 Compromises                                                                                          | 5 |

|          |                      | 5.2.2 Vital and auxiliary components                                                                       | 6 |

|          | 5.3                  | Ethics                                                                                                     | 6 |

|          |                      | 5.3.1 Legality of emulators vs. ROMs                                                                       | 6 |

|          |                      | 5.3.2 The emulator $\ldots \ldots 4$ | 6 |

|          |                      | 5.3.3 The Boot ROM                                                                                         |   |

|          |                      | 5.3.4 The ROMs                                                                                             |   |

|          |                      | 5.3.5 Test-ROMs                                                                                            |   |

|          |                      | 5.3.6 Sharing knowledge                                                                                    |   |

|          |                      |                                                                                                            |   |

|              | 5.4 | 5.3.7<br>5.3.8<br>Future | Conse | ole | Cla | ssix |  |  | • |  |  | •  | • | • | • |  |  | • | • | • | • | • | • |  | 48 |

|--------------|-----|--------------------------|-------|-----|-----|------|--|--|---|--|--|----|---|---|---|--|--|---|---|---|---|---|---|--|----|

| 6            | Con | clusion                  | IS    |     |     |      |  |  |   |  |  |    |   |   |   |  |  |   |   |   |   |   |   |  | 50 |

| Bibliography |     |                          |       |     |     |      |  |  |   |  |  | 51 |   |   |   |  |  |   |   |   |   |   |   |  |    |

# List of Figures

| $1.1 \\ 1.2$ | The first Game Boy model, DMG-01. From [9]. Public Domain<br>Diagram of the architecture of the Game Boy and the general archi-                                                                                         | 2  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|              | tecture of a game cartridge (Game Pak). From [19]. CC BY 4.0                                                                                                                                                            | 3  |

| 2.1          | Displaying the 8-bit operation codes for the LR35902, highlighting six<br>of the operation codes, showing their assembly instruction, number of<br>bytes used, number of cycles to execute and what flags are affected. |    |

| 0.0          | From [33]. Modified with permission                                                                                                                                                                                     | 7  |

| 2.2          | Visual representation of how the address space is divided in the Game Boy. From [30]. Adapted with permission.                                                                                                          | 9  |

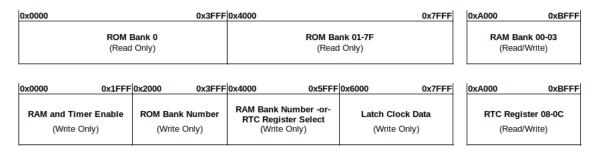

| 2.3          | Memory map of MBC3. While all MBCs do not necessarily contain<br>the same features, most follow a similar structure [42].                                                                                               | 13 |

| 2.4          | The two tile sets. Sprites may only use tiles from the tile set ranging from 0x8000 to 0x9000 while the background and window can use                                                                                   | 10 |

| ~ ~          | any of the two sets. From [30]. Used with permission                                                                                                                                                                    | 16 |

| 2.5          | What is shown on the LCD in relation to the background map. From [30]. Used with permission                                                                                                                             | 17 |

| 2.6          | The various PPU modes and their durations. From [45]. Public                                                                                                                                                            |    |

| 2.7          | Domain                                                                                                                                                                                                                  | 18 |

| 2.1          | audio channels. Bits coloured in yellow are write only and will always<br>return 1 if read from [51]. From [30]. Adapted with permission                                                                                | 22 |

| 2.8          | The registers NR52-NR50, addresses 0xFF26-0xFF24, are used for controlling the power and returns the state of all channels. Bits                                                                                        |    |

|              | coloured in yellow are write only and will always return 1 if read                                                                                                                                                      |    |

|              | from. Bits coloured in blue are read only, any data written to this location will be ignored [51].                                                                                                                      | 23 |

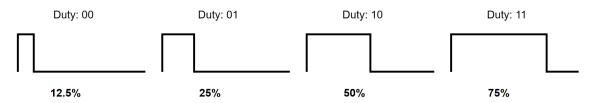

| 2.9          | The four pulse waveforms with their corresponding duties [51]. The percentages indicate what amount of the wave is high. Duty "10" is                                                                                   |    |

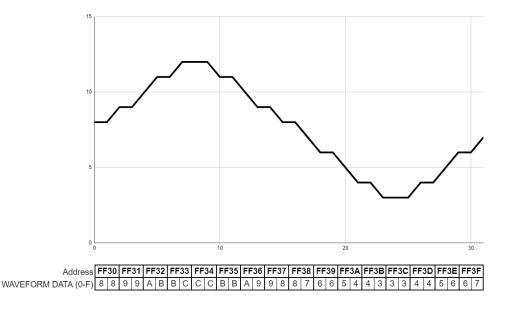

| 9 10         | most commonly usedA rough representation of how a custom waveform is created through                                                                                                                                    | 24 |

| 2.10         | addresses 0xFF30 to 0xFF3F                                                                                                                                                                                              | 25 |

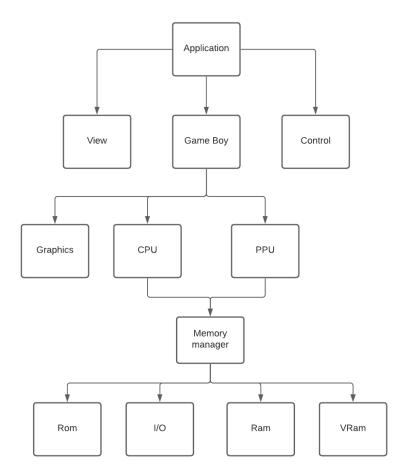

| 3.1          | Initial sketch of how different features were to be separated into different modules.                                                                                                                                   | 28 |

| 4.1          | Dependency diagram over the Game Boy module                                                                                                                                                                             | 30 |

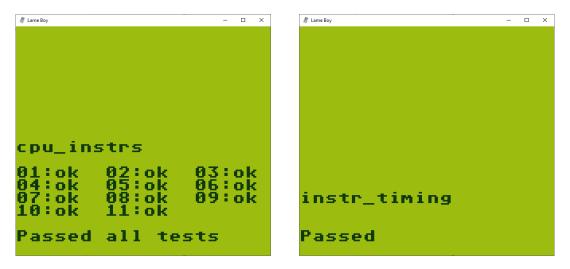

| 4.2 | Displaying the emulator results from Blargg's test ROMs checking     |    |

|-----|----------------------------------------------------------------------|----|

|     | the correctness of the CPU instructions and CPU timing respectively. | 33 |

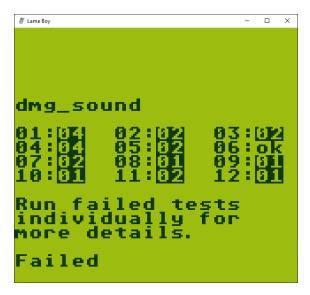

| 4.3 | Results of running the dmg_sound test ROM from Blargg's test ROMs    |    |

|     | [64]                                                                 | 40 |

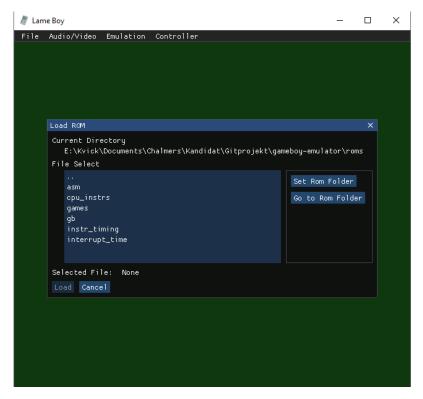

| 4.4 | A screenshot of the emulator when loading ROMs                       | 41 |

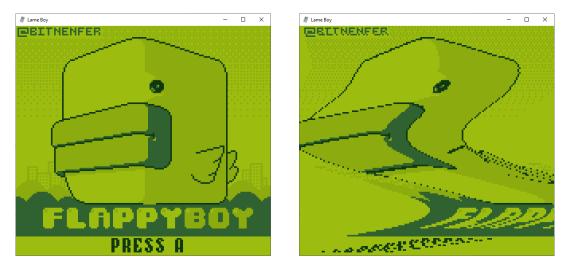

| 5.1 | The starting screen of the game Flappyboy. From left to right, its   |    |

|     | original form and its distorted form achieved by writing to the SCX  |    |

|     | and SCY registers between scanlines. From [74]. Screenshot by au-    |    |

|     | thors, used with permission                                          | 44 |

# List of Tables

| 2.1 | Layout of the button states located in memory address 0xFF00. From       | 1 1 |

|-----|--------------------------------------------------------------------------|-----|

|     | [40]. Adapted with permission                                            | 11  |

| 2.2 | Layout of the each bit in the timer control register located at address  |     |

|     | 0xFF07. From [41]. Modified with permission.                             | 12  |

| 2.3 | List of the different RTC registers and its contents. From [43]. Adapted |     |

|     | with permission                                                          | 14  |

| 2.4 | Description of the labels in Figure 2.7. From [51]. Adapted with         |     |

|     | permission.                                                              | 23  |

| 2.5 | Description of the labels in Figure 2.8. From [51]. Adapted with         |     |

|     | permission.                                                              | 23  |

| 2.6 | F, D, S, V, P, L - The value of the bits labelled with "F", "D", "S",    |     |

|     | "V", "P", "L" respectively, for each channel                             | 24  |

| 4.1 | The durations of the PPU's modes                                         | 36  |

|     |                                                                          |     |

# 1 Introduction

In this chapter, both the concept of an emulator and the Game Boy are introduced. Furthermore, the purpose of this report, which is to develop an emulator of said console is specified.

# 1.1 Emulators in general

An emulator generally refers to some kind of hardware or a piece of software which emulates the functionality of some other computer system [2] [3]. While the main goal of an emulator is to imitate another computer system, an emulator may also improve upon the original system by providing additional features or by exceeding the performance of the original system [3].

Emulators are used to bridge the gap between different kinds of hardware. For example, it is possible to, within one's operating system, run other operating systems; emulate sound hardware, such as a guitar amplifier or play video games on hardware not specifically made for said games [4]. Within the scope of this report, the term emulator refers to software used specifically to make it possible to play games on systems that are not originally intended to run these games.

# 1.2 An Introduction to the Game Boy

In 1989, Nintendo released the handheld video game console Game Boy, designed by the inventor Gunpei Yokoi [5] [6]. It was the first entry in a family of video game systems, both 8-bit and 16-bit, the last of which being the Game Boy Advance Micro which was discontinued as late as 2010 [6]. The 8-bit Game Boy is the predecessor to Nintendo's more modern handheld consoles: the Nintendo Switch [7] and The Nintendo DS (Dual Screen) [8] console family.

The 1989 Game Boy, also known as DMG-01 (Dot Matrix Game), is an 8-bit handheld console characterised by its green monochromatic LCD display and bulky grey design (see Figure 1.1) [5]. The other 8-bit Game Boy models are Game Boy Pocket, Game Boy Light and Game Boy Color. The Game Boy Pocket and Game Boy Light are slimmer versions of the DMG-01 with upgraded LCDs while Game Boy Color has a colour LCD and can play games not supported by the older Game Boys [6]. In this report Game Boy refers to either of the DMG-01, Game Boy Pocket, Game Boy Light or all of them grouped together since there are no major differences between

them. The Game Boy Color and Game Boy Advance models are not covered by this report.

Figure 1.1: The first Game Boy model, DMG-01. From [9]. Public Domain.

The Game Boy and Game Boy Color have together sold approximately 118 million units [10], making them one of Nintendo's most successful product lines ever, while also being the birthplace of popular franchises such as Kirby and Pokémon [11] [12] [13]. According to Katie Smith-Wong at the entertainment news site Den of Geek [5], there are a number of factors that led to the success of the Game Boy, the first being the design of the consoles; Compared to its competitors, the Game Boy and its variations were simplistic in their design. Because of this simplicity, the Game Boy consoles were more affordable than the competing hand held consoles while also having a longer battery life. Furthermore, multiplayer mode was possible thanks to the built in game link port. This in combination with the affordability and the superior battery life made the different Game Boys excellent multiplayer consoles. The many iconic game titles also contributed to the Game Boy's success, most notably Tetris [14] and the Pokémon [12] games, which reached out to the mainstream audience.

Recreating the behaviour of a computer system within another computer system through software is a computationally heavy task since software is much slower than electronics; therefore, simpler computer systems were the first to be emulated on personal computers through software. During the middle of the 1990s the personal computers were powerful enough to make emulation of earlier video game consoles feasible [15]. During this period Nintendo was one of the most popular media brands [16] and thus emulators for Nintendo's consoles started to appear on the internet. The first known emulator of the Game Boy released, that could run commercial games, was an emulator by the name Virtual Game Boy. It was created by Marat Fayzullin in 1995 for some unknown system and was ported to PC somewhere between 1995 and 1996 [17]. Since then many more Game Boy emulators have been released; written in many different languages and ranging in functionality [18].

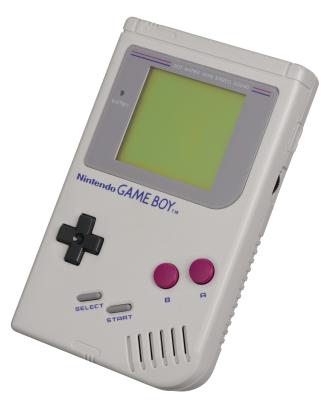

The central component of the Game Boy is the DMG-CPU [19] which is a chip containing a pixel processing unit (PPU), a central processing unit (CPU) and an audio processing unit (APU). Connected to the DMG-CPU are 8 KiB of RAM and video RAM (VRAM). The PPU outputs pixels, that can be one of four shades, to an LCD that is  $160 \times 144$  pixels in dimensions and the audio is output either through a headphone jack or a built in speaker. Games are stored on ROM chips that come inside cartridges see Figure 1.2.

Figure 1.2: Diagram of the architecture of the Game Boy and the general architecture of a game cartridge (Game Pak). From [19]. CC BY 4.0.

# 1.3 Purpose

The purpose of this thesis is to explore the possibility of developing a set of microcontrollers which can be assembled to a complete complex system. This is done through emulating the original Game Boy from 1989. As per the initial project description, focus will be on having a graphical interface working, not taking sound or other systems into account.

Developing an emulator presents additional purposes as a problem with older gaming consoles is that many of them are no longer produced and are therefore becoming harder and harder to come by. An emulator solves this problem by letting people play old console games on newer hardware. This thesis therefore aims to create a Game Boy emulator for the PC to allow future generations to have the same experience as the people playing the games on the original console whilst also preserving a piece of history. Additionally, the authors would like to share the accumulated knowledge of emulator development with others by providing documentation for the design as well as the code, so that others may learn from it and possibly use it as a base for their own emulators.

# 1.4 Delimitations

To reduce the complexity and scope of this thesis certain delimitations have been made. The thesis has been limited to only emulate the original Game Boy from 1989 and subsequent with equivalent hardware. This reduces the complexity of the thesis significantly as it reduces the amount of different systems and chips needed to be researched. Furthermore, it also means that the hardware which is to be researched is older and therefore of lower complexity than more modern hardware.

Regarding some features and systems in the Game Boy, further limitations are made. First of all; "Serial Data Transfer" is not supported. This is a feature which is used to connect a Game Boy to another Game Boy to, amongst other things, allow for multiplayer gameplay [20]. Although this could be implemented in software either by connecting two instances of the emulator on the same machine, or separate machines through internet play, this is simply not within the primary scope of emulating the Game Boy hardware.

The games for the Game Boy comes in cartridges called Game Paks [21]. The specifications of these can differ between different games with a total of 28 different configurations supported by the console, including six different memory bank controllers (MBCs) [22]. The aim is not to support all of the configurations, but rather the most significant types.

The Game Boy also has a feature called "Vin", allowing the use of external audio hardware located in the cartridge. However, none of the games made for Game Boy uses this feature [23] and is therefore excluded from being implemented in the emulator.

# 1.5 Ethics

Creating an emulator for a previously commercially sold product comes with complications. Because of Nintendo having created the Game Boy, it is natural that they are committed to making sure no one infringes the copyrights related to their product. When discussing emulators, there is also often a discussion of what is right and wrong, what counts as piracy and what is legal to do around the subject of copyright.

Nintendo Australia states the following regarding emulators [24]:

"A Nintendo emulator is a software program that is designed to allow gameplay on a platform that it was not created for. A Nintendo emulator allows for Nintendo console based or arcade games to be played on unauthorised hardware. The video games are obtained by downloading illegally copied software, i.e. Nintendo ROMs, from Internet distributors. Nintendo ROMs then work with the Nintendo emulator to enable game play on unauthorised hardware such as a personal computer, a modified console, or another video game device."

Thus, Nintendo claim that the games which are used together with emulators are obtained illegally. However, they do not explicitly state that they consider the use nor development of emulators illegal, as long as no copyrighted material is used. All of this leads to a lot of confusion around the legality and ethics of emulation, further discussion regarding this topic can be found in Section 5.3.

# 2

# Theory

This section aims to describe the various components used in the Game Boy. This is needed to then be able to understand how to properly emulate the function of those components.

# 2.1 The Central Processing Unit

The Central Processing Unit (CPU) used in the Game Boy is a Sharp LR35902 [25] [26] which is designed specifically for the Game Boy. The chip is heavily inspired by the Zilog Z80 [27] and the Intel 8080 [28]. While the CPU itself has a clock frequency of 4 MHz [25], one can consider it having an actual clock speed of 1 MHz. This is due to the fact that the CPU is bound by the speed of the memory [29] (the rate the RAM can provide data to the CPU) which has a clock speed of 1 MHz, see slide 149 of [30]. Furthermore, the CPU has a 16-bit address bus [31] and an 8-bit arithmetic logic unit (ALU).

## 2.1.1 Registers

The CPU has six general purpose registers, B, C, D, E, H and L [32]. These are all 8 bits each, but can be used pairwise as three 16-bit registers, BC, DE and HL. There are also two additional 8-bit registers, A and F, which both have specific purposes. A is the accumulator register where all the arithmetic is done. The F register, despite being 8 bits, only uses 4 bits to store the value of the four flags of the ALU. These are the zero, negative, half-carry and carry flags [32], abbreviated as Z, N, H and C respectively. Additionally, the CPU has a 16-bit program counter (PC) and stack pointer (SP).

### 2.1.2 Instruction set

In total the CPU supports 500 assembly instructions, of which 244 are 8-bit and 256 are 16-bit, see Figure 2.1 for the 8-bit instructions. For the CPU to interpret the 16-bit operations, a certain prefix is used (0xCB) found in the 8-bit table allowing the CPU to interpret the following 8 bits as an instruction from the 16-bit table. The tables specify for each instruction which flags it affects, how many bytes it is encoded with and how many machine cycles it requires to execute.

|      | x0                | ×1            | ×2                  | x3            | x4                    | ×5                | x6                 | ×7              | ×8           | x9                     | XA                 | ×В      | ×C               | xD               | xE            | xF              |

|------|-------------------|---------------|---------------------|---------------|-----------------------|-------------------|--------------------|-----------------|--------------|------------------------|--------------------|---------|------------------|------------------|---------------|-----------------|

|      | NOP               | LD BC, d16    | LD (BC), A          | INC BC        | INC B                 | DEC B             | LD B, d8           | RLCA            | LD (a16), SP | ADD HL, BC             | LD A, (BC)         | DEC BC  | INC C            | DEC C            | LD C, d8      | RRCA            |

| Θx   | 1 1               | 3 3           | 1 2                 | 1 2           | 1 1<br>Z 0 H -        | 1 1<br>Z 1 H -    | 2 2                | 1 1<br>0 0 0 A7 | 3 5          | 1 2<br>- 0 H CY        | 1 2                | 1 2     | 1 1<br>Z 0 H -   | 1 1<br>Z 1 H -   | 2 2           | 1 1<br>0 0 0 A0 |

|      | STOP              | LD DE, d16    | LD (DE), A          | INC DE        | INC D                 | DEC D             | LD D, d8           | RLA             | JR s8        | ADD HL, DE             | LD A, (DE)         | DEC DE  | INC E            | DEC E            | LD E, d8      | RRA             |

| 1×   | 2 1               | 3 3           | 1 2                 | 1 2           | 1 1                   | 1 1               | 2 2                | 1 1             | 2 3          | 1 2                    | 1 2                | 1 2     | 1 1              | 1 1              | 2 2           | 1 1             |

|      |                   |               |                     |               | Z Ø H -               | Z 1 H -           |                    | 0 0 0 A7        |              | - 0 H CY               |                    |         | Z 0 H -          | Z 1 H -          |               | 0 0 0 A0        |

|      | JR NZ, s8         | LD HL, d16    | LD (HL+), A         | INC HL        | And H                 | DEC H             | LD H, d8           | ReiDAA gulär    | JR Z, s8     | ADD HL, HL             | LD A, (HL+)        | DEC HL  | INC L            | DEC L            | LD L, d8      | CPL             |

| 2×   | 2 3/2             | 3 3           | 1 2                 | 1 2           | 1 1                   | 1 1               | 2 2                | 1 1<br>Z - 0 CY | 2 3/2        | 1 2                    | 1 2                | 1 2     | 1 1              | 1 1              | 2 2           | 1 1             |

|      | JR NC. s8         | LD SP. d16    | LD (HL-), A         | INC SP        | Z 0 H -<br>INC (HL)   | Z 1 H<br>DEC (HL) | LD (HL)            |                 | JR C. 58     | - 0 H CY<br>ADD HL, SP | LD A. (HL-)        | DEC SP  | Z 0 H -<br>INC A | Z 1 H -<br>DEC A | LD A, d8      | - 1 1 -<br>CCF  |

| 3x   | 2 3/2             | 3 3           | 1 2                 | 1 2           | 1 3                   | 1 3               | 1 3                | SUP             | 2 3/2        | 1 2                    | 1 2                | 1 2     | 1 1              | 1 1              | 2 2           | 1 1             |

|      |                   |               |                     |               | z ө н -               | Z 1 H -           |                    | - 0 0 1         |              | - 0 H CY               |                    |         | Z 0 H -          | Z 1 H -          |               | - 0 0 ICY       |

|      | LD B, B           | LD B, C       | LD B, D             | LD B, E       | LD B, H               | LD B, L           | LD B, (HL)         | LD B, A         | LD C, U      | LD C, C                | LD C, D            | LD C, E | LD C, H          | LD C, L          | LD C, (HL)    | LD C, A         |

| 4×   | 1 1               | 1             | 1 1                 | 1 1           | 1 1                   | 1 1               | 1 2                | 1 1             | 1 1          |                        | 1 1                | 1 1     | 1 1              | 1 1              | 1 2           | 1 1             |

|      | LD D, B           | LD D. C       | LD D, D             | LD D. E       | LD D, H               | LD D, L           | LD D, (HL)         | LD D, A         | LD E, B      | LD E, C                | LD E. D            | LD E, E | LD E, H          | LD E, L          | LD E, (HL)    | LD E, A         |

| 5×   | 1 1               | 1 1           | 1 1                 | 1 1           | 1 1                   | 1 1               | 1 2                | 1 1             | 1 1          | 1 1                    | 1 1                | 1       | 1 1              | 1 1              | 1 2           | 1 1             |

|      |                   |               |                     |               |                       |                   |                    |                 |              |                        |                    |         |                  |                  |               |                 |

|      | LD H, B           | LD H, C       | LD H, D             | LD H, E       | LD H, H               | LD H, L           | LD H, (HL)         | LD H, A         | LD L, B      | LD L, C                | LD L, D            | LD L, E | LD L, H          | 10 L, L          | LD L, (HL)    | LD L, A         |

| 6x   | 1 1               | 1 1           | 1                   | 1 1           | 1 1                   | 1 1               | 1 2                | 1 1             | 1 1          | 1 1                    | 1 1                | 1 1     | 1 1              | 1 1              | 1 2           | 1 1             |

|      | LD (HL), B        | LD (HL), C    | LD (HL), D          | LD (HL), E    | LD (HL), H            | LD (HL), L        | HAU                |                 |              |                        |                    |         |                  |                  |               | LD A, A         |

| 7×   | 1 2               | 1 2           | 1 2                 | 1 2           | 1 2                   | 1 2               | 1                  | LD HL           | d16          | LD                     | ) (HL 1            | -), A   |                  | INC H            |               | 1 1             |

|      |                   |               |                     |               |                       |                   |                    |                 | , uro        |                        | / (IIL-1           | ), ¬    |                  | тис п            | -             |                 |

|      | ADD A, B<br>1 1   | ADD A, C      | ADD A, D<br>1 1     | ADD A,<br>1 1 | ADD A, H<br>1 1       | ADD A, L<br>1 1   | ADD A,             | 3               | 3            |                        | 1                  | 2       |                  | 1 2              | ,             | ADC A, A<br>1 2 |

| ox   | ZOHCY             | Z Ө Н СҮ      | Z Ө Н СҮ            | z ө н сү      | z ө н сү              | z ө н сү          | ZØN                | 2               | 2            |                        | ±                  | 2       |                  | 1 2              |               | ZOHCY           |

|      | SUB B             | SUB C         | SUB D               | SUB E         | ив н                  | SUB L             | SUB                |                 |              |                        |                    |         |                  |                  |               | SBC A, A        |

| 9×   | 1 1               | 1 1           | 1 1                 | 1 1           | 1 1                   | 1 1               | 1                  |                 |              |                        |                    |         |                  |                  | -             | 1 1             |

|      | Z 1 H CY          | Z 1 H CY      | Z 1 H CY            | Z 1 H CY      | ZIHC                  | Z 1 H CY          | Z 1 8              |                 |              | _                      |                    |         |                  |                  |               | Z 1 H CY        |

| 0~   | AND 8<br>1 1      | AND C<br>1 1  | AND D<br>1 1        | AND E<br>1 1  | AND H                 | AND L<br>1 1      | AND (              | LD SP           | d16          |                        | ) (HL-             | Δ (·    |                  | INC S            | P             | XOR A<br>1 1    |

|      | z 0 1 0           | Z 0 1 0       | z 0 1 0             | z 0 1 0       | z 0 1 0               | 2910              | ze                 | 20 31           | , uro        |                        | (112               | /, ~    |                  | THC D            |               | zeee            |

|      | OR B              | OR C          | OR D                | OR E          | OR H                  | OR                | OR (               | 3               | 3            |                        | 1                  | 2       |                  | 1 2              | ,             | CP A            |

| B×   | 1 1               | 1 1           | 1 1                 | 1 1           | 1 1                   | 1 1               | 1                  | 5               | 5            |                        | -                  | 2       |                  |                  |               | 1 1             |

|      | Z 0 0 0           | Z 0 0 0       | Z 0 0 0             | Z 0 0 0       | Z 0 0 0               | 2000 <b>-</b>     | ZØ                 |                 |              |                        |                    |         |                  |                  |               | Z 1 H CY        |

| c×   | RET NZ<br>1 5/2   | POP BC<br>1 3 | JP NZ, a16<br>3 4/3 | JP a16<br>3 4 | CALL NZ, a16<br>3 6/3 | PUSH BC<br>1 4    | AND A              |                 |              |                        |                    | -       | -                |                  | -             | RST 1<br>1 4    |

| _    |                   | · · · · ·     | 3 4/3               |               |                       |                   | ZOHCY              |                 |              |                        |                    |         |                  |                  | ZƏHCY         |                 |

|      | RET NC            | POP DE        | JP NC, a16          |               | CALL NC, a16          | PUSH DE           | SUB d8             | RST 2           | RET C        | RETI                   | JP C, a16          |         | CALL C, a16      |                  | SBC A, d8     | RST 3           |

| Dx   | 1 5/2             | 1 3           | 3 4/3               |               | 3 6/3                 | 14                | 22                 | 1 4             | 1 5/2        | 14                     | 3 4/3              |         | 3 6/3            |                  | 2 2           | 1 4             |

|      |                   |               |                     |               |                       |                   | Z 1 H CY<br>AND d8 |                 | ADD SP. 58   |                        |                    |         |                  |                  | Z 1 H CY      |                 |

| Ex   | LD (a8), A<br>2 3 | POP HL<br>1 3 | LD (C), A<br>1 2    |               |                       | PUSH HL<br>1 4    | AND d8<br>2 2      | RST 4<br>1 4    | ADD SP, 58   | 3P HL<br>1 1           | LD (a16), A<br>3 4 |         |                  |                  | XOR d8<br>2 2 | RST 5<br>1 4    |

|      |                   |               |                     |               |                       |                   | Z 0 1 0            | 1.1.            | 0 0 H CY     |                        |                    |         |                  |                  | z 0 0 0       |                 |

|      | LD A, (a8)        | POP AF        | LD A, (C)           | DI            |                       | PUSH AF           | OR d8              | RST 6           | LD HL, SP+s8 | LD SP, HL              | LD A, (a16)        | EI      |                  |                  | CP d8         | RST 7           |

| Fx   | 2 3               | 1 3           | 1 2                 | 1 1           |                       | 14                | 2 2                | 1 4             | 2 3          | 1 2                    | 34                 | 1 1     |                  |                  | 2 2           | 14              |

| - 11 |                   |               |                     |               |                       |                   | Z 0 0 0            |                 | 0 0 H CY     |                        |                    |         |                  |                  | Z 1 H CY      |                 |

Figure 2.1: Displaying the 8-bit operation codes for the LR35902, highlighting six of the operation codes, showing their assembly instruction, number of bytes used, number of cycles to execute and what flags are affected. From [33]. Modified with permission.

# 2.1.3 Interrupts

Like many other CPUs, the Sharp LR35902 supports interrupts. Interrupts are used in order to break the regular flow of the CPU, forcing it to handle the interrupt before returning to what it was doing previously. Different interrupts have different pre-defined addresses where the respective interrupt routines are stored [34]. When an interrupt occurs, the CPU executes the interrupt routine, and then continues execution from the address that was current when the interrupt occurred. The existing interrupts and their functionalities are the following [34]:

- V-blank An interrupt sent from the PPU when it has created a whole frame and wants to draw it, for more information see Section 2.3.

- LCD STAT A customisable interrupt regarding various conditions of the PPU. An interrupt is generated any time the PPU goes from not meeting any condition to meeting at least one condition. Which conditions are used is determined by the STAT register of the PPU, for more information, see Section 2.3.3

- Timer Sends an interrupt request when a set timer has run out, for more information see Section 2.2.8.

- Serial The serial transfer interrupt which handles the communication between two Game Boys when they are connected through the serial port. This is not implemented, as is explained in Section 1.4.

- Joypad An interrupt which handles the input from the joypad, for more information see Section 2.2.7.

The interrupts are implemented by having three different types of flag registers [34]:

- IME Interrupt Master Enable. This flag enables and disables all other interrupt flags. Can only be manipulated through specific instructions.

- IE Interrupt Enable. Enables or disables a specific flag. Consists of five bits, one for each type of interrupt. Manipulated through memory, located at OxFFFF.

- IF Interrupt Flag. Shows that an interrupt has been requested. This is the flag which is set when an interrupt is raised. The register consists of five bits, one for each type of interrupt. Manipulated through memory, located at OxFFOF.

If IME is disabled, IE and IF can still be altered, but they are not acted upon until IME is enabled once again. For an interrupt to occur and be handled by the CPU three things therefore need to happen: both the IME flag and a specific IE flag must be enabled, and the corresponding IF flag must be triggered [34].

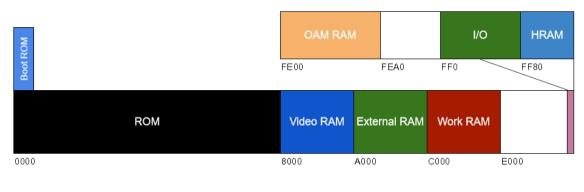

# 2.2 Memory and I/O devices

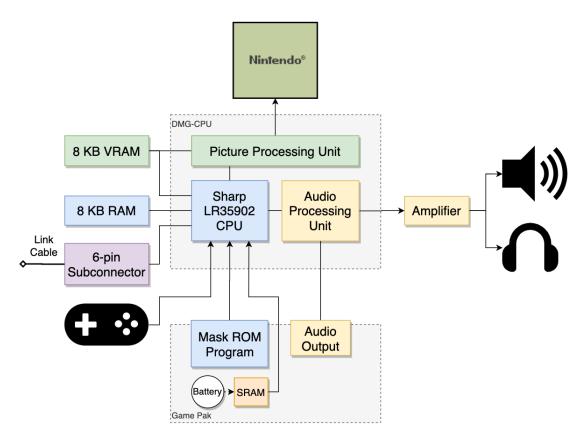

The CPU needs to access memory and communicate with peripheral devices. To achieve this the Game Boy uses a 16-bit address bus and an 8-bit data bus [35]. The memory and different peripheral devices are mapped to specific memory addresses visualised in Figure 2.2.

0 KiB

64 KiB

Figure 2.2: Visual representation of how the address space is divided in the Game Boy. From [30]. Adapted with permission.

In the Game Boy's 64 KiB address space, different address ranges are used for different purposes. Below is a description of how this is handled. Note that the I/O devices are controlled through manipulating address space and that the more complex I/O devices, the PPU and APU, are described in Section 2.3 and Section 2.4 respectively.

## 2.2.1 Boot ROM

#### Address: 0x00 - 0xFF

The boot ROM is a 256 byte ROM located on the DMG-CPU and contains the code that is executed when the Game Boy is powered on [36]. The purpose of the boot ROM is to initialise the different hardware units and prepare the Game Boy to execute game code [37]. The official boot ROM used on the Game Boy does this while scrolling down the Nintendo logotype. The use of copyrighted material on the boot ROM has legal implications which is further discussed in Section 5.3. In practice the boot ROM is only accessible a short time when the Game Boy is powered on due to the fact that it disables itself after it has been run. Disabling the boot ROM is done by storing a non-zero value at memory address 0xFF50 and will map the addresses to the ROM instead, see the overlap in Figure 2.2.

# 2.2.2 ROM

#### Address: 0x0000 - 0x7FFF

The ROM located in the Game Boy's memory map is the area where the interactions with data from the inserted game ROMs happen [31]. Although the allocated size for the ROM on the Game Boy is only 32 KiB, the ROMs it supports can be much larger. This is possible through the use of bank switching using a Memory Bank Controller (MBC) [38], located in the Game Pak ROM, see Section 2.2.10 for more information.

# 2.2.3 Video RAM

#### Address: 0x8000 - 0x9FFF

The Video RAM (VRAM) is an 8 KiB RAM [31] that is accessible by both the CPU and PPU. It it used by the CPU to store data which the PPU uses for drawing. While the PPU is drawing, it is reading from the VRAM and the CPU is therefore not allowed access. For more information regarding how the VRAM is used, see Section 2.3.

# 2.2.4 External RAM

### Address: 0xA000 - 0xBFFF

The external RAM (XRAM) is an optional memory that is located on some of the game cartridges. Its size varies from game to game and can, if desired, also make use of bank switching (see Section 2.2.10). The XRAM is often used for saving progress and high score tables [31]. This is done by powering the XRAM with a small battery inside the game cartridge to make sure the data is conserved between different gaming sessions.

## 2.2.5 WRAM

#### Address: 0xC000 - 0xDFFF

The Work RAM (WRAM) is the main memory of the system which is used by the CPU to store any data the game uses while running. The WRAM is located on the DMG-CPU and has a size of 8 KiB [31].

## 2.2.6 OAM RAM

#### Address: 0xFE00 - 0xFE9F

The Object Attribute Map (OAM) is the area where sprite data is stored. The OAM is divided into 40 blocks of four bytes each with each block corresponding to a sprite. Both the PPU and CPU have direct access to this memory area. While the PPU is rendering scanlines, the CPU has limited access to this area [39]. The CPU can also transfer data into the OAM through the use of Direct Memory Access (DMA) transfers, this process is described in detail in Section 2.3.5.

# 2.2.7 Joypad

#### Address: 0xFF00

The Joypad is the device that connects the user's input with the system. There are eight buttons on the Game Boy, four directional buttons: up, down, left and right, and four action buttons: A, B, Start and Select. The buttons have two states, pressed or not pressed. These states of the buttons are stored at address 0xFF00 as a 2x4 matrix [40].

By writing specific values to bit 4 and 5 either the action buttons or directional buttons will be selected. When selecting either the action or direction buttons bit 0-3 will correspond to the selected buttons [40]. See Table 2.1.

Bit 7 - Not used Bit 6 - Not used Bit 5 - Select Action buttons (0=Select) Bit 4 - Select Direction buttons (0=Select) (O=Pressed) (Read Only) Bit 3 - Input: Down or Start Bit 2 - Input: Up (O=Pressed) (Read Only) or Select Bit 1 - Input: Left or B (0=Pressed) (Read Only) Bit 0 - Input: Right or A (O=Pressed) (Read Only)

**Table 2.1:** Layout of the button states located in memory address 0xFF00. From [40]. Adapted with permission.

When a button is pressed, an interrupt is raised, but only if the pressed button is a button that is selected by bit 4 and 5 (either an action or a directional button) [40]. Regarding how to actually handle the joypad input, it is up to the developer to either poll the  $2 \times 4$  -matrix or by using the interrupts.

## 2.2.8 Timer

### Address: 0xFF04 - 0xFF07

The Game Boy has a built-in timer which can be used to perform time sensitive tasks. It is used and controlled by reading and writing to the following registers [41]:

#### Divider Register - DIV Address: 0xFF04

The DIV register is a counter that always increments at a rate of 16384Hz. When writing any value to the address the counter resets to 0 [41].

#### Timer counter - TIMA Address: 0xFF05

This is another counting register, it increments at the rate that is specified in the TAC register. When the counter value is 0xFF and overflows it is reset to the value in TMA as the new counter value. When the counter overflows the "Timer"-interrupt is raised [41]. Writing to this register simply changes the counter to the written value.

# Timer Modulo - TMA

#### Address: 0xFF06

This register holds the timer modulo value. This value is loaded into the TIMA register when the TIMA counter overflows [41]. It can be used to further modify the chosen clock speed chosen in the TAC register.

#### Timer Control - TAC

#### Address: 0xFF07

This register is used to control the timer. By writing to this register the timer can be enabled or disabled. The rate at which the TIMA register will increment can also be controlled by writing to this register [41].

As shown in Table 2.2, bit 2 enables or disables the timer. Notice that disabling the timer does not stop the DIV counter. Bits 0 and 1 are used to select one out of four possible clock speeds; 4069 Hz, 262144 Hz, 65536 Hz or 16384 Hz [41].

```

Bit 2 - Timer Enable

Bits 1-0 - Input Clock Select

00: CPU Clock / 1024 (4096 Hz)

01: CPU Clock / 16 (262144 Hz)

10: CPU Clock / 64 (65536 Hz)

11: CPU Clock / 256 (16384 Hz)

```

Table 2.2: Layout of the each bit in the timer control register located at address 0xFF07. From [41]. Modified with permission.

### 2.2.9 HRAM

#### Address: 0xFF80 - 0xFFFE

The high RAM or HRAM is very much like the WRAM although it is much smaller and faster to access. It is faster because of a special instruction that assumes that the highest byte in the address is 0xFF and therefore saves time decoding the instruction [33]. During a DMA-transfer (see Section 2.3.5) the CPU is limited to use only this memory. The size of the HRAM is 126 bytes [31].

# 2.2.10 Memory Bank Controllers

As previously mentioned, the Game Boy uses a 16-bit address bus, which in turn limits the memory addresses available for the game ROM and external RAM. To bypass this limitation many game cartridges make use of a memory bank controller (MBC). The MBC is used to map different sections of a memory, called memory banks, to one specific address range, this method is called bank switching. It works as follows: reading from addresses 0x0000 to 0x7FFF returns a byte stored on the ROM as expected, but writing to those same addresses will instead change the MBC's control registers, this is further described below and in Figure 2.3. These control registers control what memory bank is to be used for both the game ROM and the external RAM (if any).

There are different versions of MBCs which all support various arrangements of additional hardware. Examples of such hardware are external RAM with or without a battery powering said RAM and in some cases also a timer [42]. For example, MBC3 supports up to 2 MiB of ROM and/or 64 KiB of RAM, and Real Time Clock (RTC) with battery [42].

Figure 2.3: Memory map of MBC3. While all MBCs do not necessarily contain the same features, most follow a similar structure [42].

The following is a description of the structure and functionality of MBC3, shown in Figure 2.3 [42]:

### ROM Bank 0

Contains the first 16 KiB of the ROM.

#### ROM Bank 0x01-0x7F

This part of the memory is used for bank switching. There are at most 127 available memory banks each with a size of 16 KiB, resulting in a total ROM size of  $128 \times 16$  KiB = 2 MiB, including ROM bank 0.

#### **RAM and Timer Enable**

Writing specific values to this address will enable reading and writing to XRAM or RTC registers depending on which is currently active.

#### ROM Bank Number

Writing to this address controls which ROM bank is in use.

#### RAM Bank Number/RTC Register Select

Writing to this area maps the corresponding XRAM bank or RTC register into the memory of 0xA000-0xBFFF.

#### RAM Bank 0x00-0x03 or RTC Register 0x08-0x0C

Depending on the current **Bank Number/RTC Register selection**, this memory space is used to either access an 8 KiB external RAM Bank, or a single RTC Register, see Table 2.3.

#### Latch Clock Data

If writing first 0x00, and then 0x01 to this register, the current time becomes latched into the RTC register. This means that the current time can be read from the register while the RTC continues to tick. Additionally the RTC needs a quartz oscillator as well as an external battery to work while the Game Boy is turned off.

0-59 (0x00-0x3B) 0x8 RTC S Seconds Ox9 RTC M Minutes 0-59 (0x00-0x3B) OxA RTC H Hours 0-23 (0x00-0x17) OxB RTC DL Lower 8 bits of Day Counter (0x00-0xFF) OxC RTC DH Upper 1 bit of Day Counter, Carry Bit, Halt Flag Most significant bit of Day Counter (Bit 8) Bit O Halt (0=Active, 1=Stop Timer) Bit 6 Day Counter Carry Bit (1=Counter Overflow) Bit 7

**Table 2.3:** List of the different RTC registers and its contents. From [43]. Adapted with permission.

# 2.3 The Pixel Processing Unit

The purpose of the Pixel Processing Unit (PPU) is to interpret the data residing in VRAM and compose it into a picture which can then be printed on the LCD. The CPU can communicate with the PPU either by loading data into the VRAM or by reading from or writing to a number of hardware registers, most notably the LCD control and status registers. The PPU, on the other hand, uses interrupts to communicate with the CPU [44].

## 2.3.1 Composing the frame

The frame is composed of three layers: Background, Window and Sprites, rendered in that order. These layers are in turn composed of tiles, 8x8 bitmaps of colour indices, which are stored in VRAM. When rendering the picture, these indices map to one of the four colours using palette tables, which in the original Game Boy was four shades of grey over a green background [19]. The following is a description of the components used to form the frame.

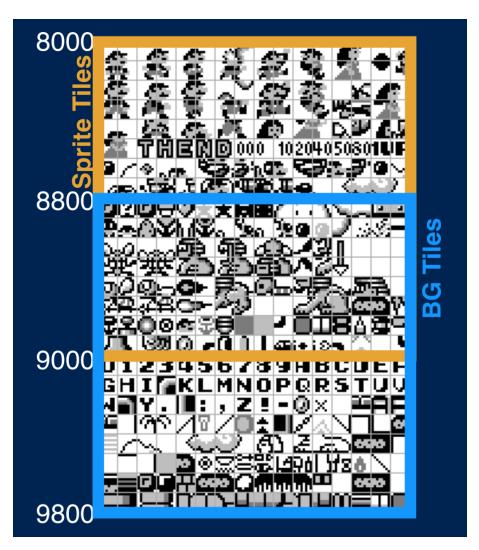

**Tiles** - As previously mentioned, the tiles are 8x8 bitmaps stored in RAM, 16 bytes per tile. This is because each row of a tile is formed by combining the bits of two bytes. The bytes are organised in two memory regions called *Tile sets*; one ranging from 0x8000 to 0x9000 and one ranging from 0x8800 to 0x9800, see Figure 2.4. These two tile sets overlap and which one to use is determined by a bit in the LCD Control register (LCDC). The first of the two uses unsigned addressing for tile IDs, while the second one uses signed addressing. [19].

Figure 2.4: The two tile sets. Sprites may only use tiles from the tile set ranging from 0x8000 to 0x9000 while the background and window can use any of the two sets. From [30]. Used with permission.

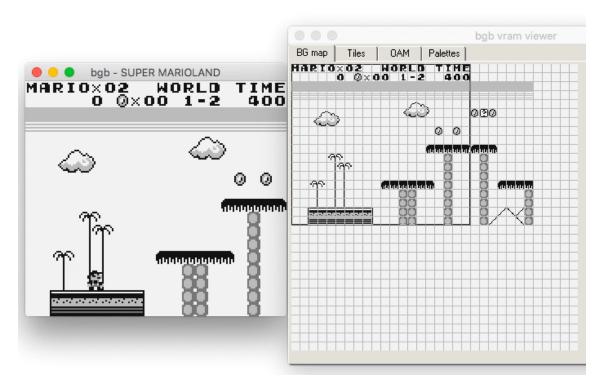

**Background** - The background is defined by a map of 32x32 tile IDs. Since a tile is 8x8 pixels, this results in a map of 256x256 pixels; however, the Game Boy's display is only 160x144 pixels. The result of this is that only part of the background is being displayed at any given time, as shown in Figure 2.5. Which part of the map to display is determined by the two hardware registers, SCX and SCY, which specify which pixel should appear in the top left corner of the display. If the edge of the map is reached, the map loops around and continues at the opposite side. There are also two maps available at any given time, which one is being used is determined by a bit in the LCDC [44].

Figure 2.5: What is shown on the LCD in relation to the background map. From [30]. Used with permission.

**Window** - The window is drawn on top of the background. Just like the background, it consists of a map of tiles; however, this map is only 20x18 tiles, just covering the entire screen and, unlike the background, does not loop around. This layer can be used to display information that should not scroll with the rest of the background, such as a GUI [44].

**Sprites** - Sprites are objects that can move around on the screen freely. They consist of one or two tiles, depending on a bit in the LCDC register. As opposed to the tiles in the background and window layers, sprites can have transparent pixels, meaning that the background and window are still visible through said pixels. Sprites only consist of tiles from the tile set ranging from 0x8000 to 0x9000, as shown in Figure 2.4 [44].

Sprite data is stored in a memory region called the Object Access Map(OAM). Each sprite takes up four bytes of memory. These bytes store the sprites' x and y coordinates, the sprites' tile IDs and a set of flags. The flags describe which of two object palettes the sprite uses, whether the sprite is flipped horizontally or vertically, and lastly whether the sprite should be drawn in front of or "behind" the background. Drawing a sprite "behind" the background results in background and window pixels with colour indices 1-3 being drawn in front of the sprite, though the sprite is still drawn in front of pixels with colour index 0 [44].

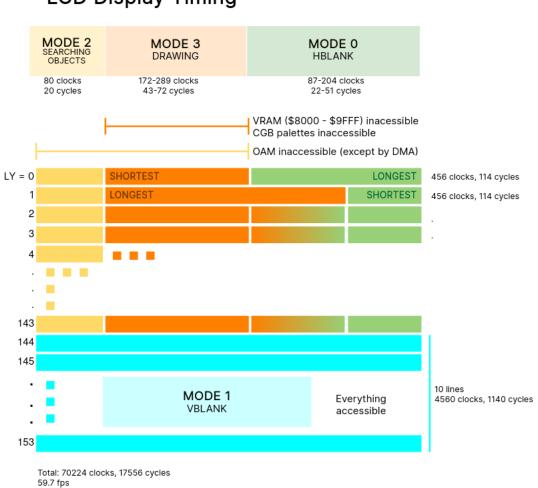

# 2.3.2 The modes

At any given time, the PPU is in one of four modes: horizontal blanking, vertical blanking, OAM search or drawing [44].

# LCD Display Timing

Figure 2.6: The various PPU modes and their durations. From [45]. Public Domain.

Depending on which mode the PPU is in, there are limits on whether the CPU has direct access to VRAM and OAM. When the CPU does not have access to one of these regions, any write to that region will be ignored and any read will return 0xFF. The PPU changes modes according to Figure 2.6 [44]. The four modes will now be described in further detail.

### Horizontal blanking

The PPU enters a horizontal blank (H-blank) whenever it has finished drawing a line. During this period, the CPU can access VRAM and OAM freely. Depending on how long the PPU was in mode 3 before entering this mode, the length of the H-blank is adjusted so that the total time spent on OAM search, drawing and H-blanking for each line is exactly 114 cycles [44].

#### Vertical blanking

The PPU enters a vertical blank (V-blank) whenever all 144 scanlines have been drawn to the screen. The V-blank is treated as ten blank lines and therefore lasts for 1140 cycles. During this time the CPU has free access to VRAM and OAM [44].

#### OAM search

The PPU enters this mode before drawing each line. When in this mode, the PPU finds the first ten sprites in OAM that intersect the current scanline to prepare for the draw phase. During this time the CPU can access VRAM freely [44].

### Drawing

The PPU enters this mode after having finished OAM search. During this mode the PPU combines the background, window and sprites of the current row and draws the pixels to the LCD. The process is described in more detail in Section 2.3.4. During this time the CPU can access neither VRAM nor OAM [44].

## 2.3.3 The registers

The PPU contains a variety of hardware registers. These are described in this section, also noting whether they are used for reading or writing to.

#### LCD Control Register (R/W)

The LCDC register is the main way for the CPU to control the operation of the PPU. It can be modified at any time and contains the following bits [46]:

- Bit 7 LCD enable. If this bit is 0, the display is off.

- Bit 6 Window tile map select. This bit determines which map should be used for the window layer.

- Bit 5 Window enable. This bit determines whether the window layer should be drawn or not.

- Bit 4 Tile set select. This bit determines which tile set should be used by the tile maps.

- Bit 3 Background tile map select. This bit determines which map should be used for the background layer.

- Bit 2 Object size. This bit determines whether sprites consist of one or two tiles.

- Bit 1 Object enable. This bit determines whether sprites should be drawn or not.

- Bit 0 Background and window enable. This bit determines whether the background and window layers should be drawn or not.

#### LCD Status and Configuration Register (R/W)

The STAT register represents the status of the PPU. It can also be used to create custom interrupts, depending on the status of the PPU. The STAT register contains the following bits [47]:

- Bit 6 LYC interrupt enable. Enables interrupts when the current scanline equals the value of the LYC register.

- Bit 5 OAM search interrupt enable. Enables interrupts when the PPU enters OAM search.

- Bit 4 V-blank interrupt enable. Enables interrupts when the PPU enters a V-blank.

- Bit 3 H-blank interrupt enable. Enables interrupts when the PPU enters an H-blank.

- Bit 2 LYC=LY flag. Is set to 1 if the current scanline equals the value of the LYC register.

- Bit 1-0 Mode flag. Represents the current mode of the PPU.

The PPU also has a variety of utility registers, described here [44]:

- SCY and SCX (Scroll X & Y) Control background scrolling. Represents the coordinate on the background map that should be displayed in the top left corner of the display. (R/W)

- LY (Line Y) Keeps track of the current scanline. (R)

- LYC (Line Y Compare) Used in the STAT register to generate interrupts. (R/W)

- WY and WX (Window X & Y) Represents the coordinate on the display where the top left pixel of the window should be displayed. (R/W)

- BGP (Background Palette) The palette for the background. Maps the indices 0-3 to white (0), light grey (1), dark grey (2) or black (3). (R/W)

- OBP0 (Object Palette 0) The first of two sprite palettes. Functions similarly to BGP except colour index 0 represents transparent pixels. (R/W)

- OBP1 (Object Palette0) The second of two sprite palettes. Functions exactly like OBP0.  $\rm (R/W)$

- DMA (Direct Memory Access) Used for triggering a DMA transfer. More information can be found in Section 2.3.5. (R/W)

## 2.3.4 Drawing the image

During mode 3 the PPU continuously transfers pixels to the LCD. This is done by loading tile data into two FIFO queues, one row of pixels at a time. One queue stores background and window pixels and the other queue stores sprite pixels. The pixels are then popped from the queues and mixed depending on whether the sprite or the background should have priority [48]. This is also where the colour indices are mapped to colours using the palette tables. Depending on how many sprites are on the current scanline and whether the background is scrolled or not, the duration of mode 3 may be lengthened or shortened [48]. This results in mode 3 lasting between 43-72 cycles, as shown in Figure 2.6.

### 2.3.5 Direct Memory Access transfer

As mentioned previously, the CPU can access OAM freely during H-blanks and Vblanks. There is however another way to update the OAM: through Direct Memory Access transfers (DMA transfers). A DMA transfer is triggered by writing a value between 0x00 and 0xDF to the DMA register [49]. This value is bit-shifted to the left eight times and is then used as the start address for the transfer, where the PPU copies the  $40 \times 4 = 160$  following bytes into the OAM. During the transfer, which takes 160 cycles, the CPU can only access HRAM and no sprites are displayed. This process can be used no matter which mode the PPU is in, though there may be visual bugs if a transfer is started when the PPU is in mode 3 [49].

# 2.4 The Audio Processing Unit

The role of the Audio Processing Unit (APU) is to play audio. The Game Boy can play sound through four separate channels, each of which is an independently controllable source of sound [50]. Each individual channel has a designated waveform assigned to it with each waveform defining what type of sound the respective channel plays. A waveform can be visually represented through a graph that shows change of amplitude over time. These waveforms sound drastically different to each other, which makes for a highly customisable sound experience even with only four channels available. The first two channels are only able to play pulse waves (see Figure 2.9), the third channel has a programmable waveform, which enables some customisability for the game developer, and the fourth channel plays a pseudo-random waveform, producing noise [51]. For further information about how waveforms and sound in general works, see [52] and [53].

#### 2.4.1 The registers

The APU has a large number of registers for controlling the audio output for each channel. Settings such as volume and frequency can be changed by writing to the registers of each channel. The layout of these registers can be seen in Figure 2.7. The labels for each bit in Figure 2.7 corresponds to a specific functionality described in Table 2.4.

|         | Control<br>4  | Frequency<br>3   | Volume<br>2      | Length<br>1       | Sweep<br>0      |

|---------|---------------|------------------|------------------|-------------------|-----------------|

| Pulse 1 | TLFFF<br>NR14 | FFFFFFFFF        | VVVVAPPP<br>NR12 | DDLLLLLLL<br>NR11 | PPPNSSS<br>NR10 |

| Pulse 2 | TLFFF<br>NR24 | FFFFFFFF         | VVVVAPPP<br>NR22 | DDLLLLLL<br>NR21  | NR20            |

| Wave    | TLFFF<br>NR34 | FFFFFFFF         | V V NR32         | LLLLLLLL<br>NR31  | E NR30          |

| Noise   | TL<br>NR44    | SSSSWDDD<br>NR43 | VVVVAPPP<br>NR42 |                   | NR40            |

Figure 2.7: The registers NR10-NR44, addresses 0xFF10-0xFF23, for controlling audio channels. Bits coloured in yellow are write only and will always return 1 if read from [51]. From [30]. Adapted with permission.

There is also a set of APU master control registers which affects the four audio channels. These can turn the whole APU on or off, indicate what channel is currently playing, and control what side the sound should come from which results in stereo sound. The layout of these registers can be seen in Figure 2.8. The labels for each bit in Figure 2.8 corresponds to a specific functionality described in Table 2.5.

| Label                     | Name               | Functionality                                                          |  |

|---------------------------|--------------------|------------------------------------------------------------------------|--|

| Т                         | Toggle             | Turns the channel on or off                                            |  |

| L (NRx4)                  | Length enable      | If the channel should be<br>turned off after a short<br>period of time |  |

| F                         | Frequency          |                                                                        |  |

| S, W, D (NR43)            | Clock Shift        | How long to play                                                       |  |

|                           | LFSR mode          | each audio sample                                                      |  |

|                           | Divisor code       |                                                                        |  |

| V, A, P (Not NR32) Volume |                    | Initial channel volume and how                                         |  |

|                           | Add mode<br>Period | Initial channel volume and how<br>it should sweep up or down           |  |

| V (NR32)                  | Volume code        | Channel volume                                                         |  |

| D (NR11,NR21)             | Duty               | Sets pulse length, see Section 2.4.3                                   |  |

| L (NRx1)                  | Length             | Time until channel is turned off                                       |  |

| P, N, S (NR10)            | Sweep period       | Sweeps channel frequency                                               |  |

|                           | Negate             | up or down to                                                          |  |

|                           | $\mathbf{Shift}$   | create sound effects                                                   |  |

| Е                         | DAC power          | Turns channel DAC on or off                                            |  |

**Table 2.4:** Description of the labels in Figure 2.7. From [51]. Adapted with permission.

Figure 2.8: The registers NR52-NR50, addresses 0xFF26-0xFF24, are used for controlling the power and returns the state of all channels. Bits coloured in yellow are write only and will always return 1 if read from. Bits coloured in blue are read only, any data written to this location will be ignored [51].

| Label | Name         | Functionality                                       |

|-------|--------------|-----------------------------------------------------|

| Р     | Power        | Enables or disables the entire APU                  |

| S     | State        | State of each channel, if 1, the channel is playing |

| L     | Left enable  | Enables or disables left and                        |

| R     | Right enable | right side for each channel                         |

**Table 2.5:** Description of the labels in Figure 2.8. From [51]. Adapted with permission.

## 2.4.2 Events

The registers described above trigger events at different frequencies. At what frequency these events should be triggered and exactly what happens at these events is controlled by the registers. Note that all values which are changed with these events are reset when the bit labelled with "T" is set [51]. The table below summarises the events which occur and at what frequency.

| Event                     | Frequency [Hz]                | Action                                                                                                |  |

|---------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------|--|

| Play sample               | 0x20000/(0x800-F)             | Play next audio sample                                                                                |  |

| Play sample (Noise)       | $0$ x80000/ $(D * 2^{(S+1)})$ | Play next audio sample                                                                                |  |

| Volume envelope           | 0x40/P                        | $V = \begin{cases} V - 1 & \text{if } \mathbf{A} = 0\\ V + 1 & \text{if } \mathbf{A} = 1 \end{cases}$ |  |

| Length sweep              | 0x100                         | Decrease L if length is enabled                                                                       |  |

| Frequency sweep (Pulse 1) | 0x80/P                        | $F = \begin{cases} F + F/2^S & \text{if N} = 0\\ F - F/2^S & \text{if N} = 1 \end{cases}$             |  |

**Table 2.6:** F, D, S, V, P, L - The value of the bits labelled with "F", "D", "S", "V", "P", "L" respectively, for each channel.

## 2.4.3 The audio data